# FPGAを用いた high-resolution TDCの開発

# Development of high-resolution TDC based on FPGA.

阪大理, 東北大理<sup>A</sup>, JAEA<sup>B</sup>, KEK<sup>C</sup>, Open-It<sup>D</sup>

@本多良太郎, 三輪浩司<sup>A</sup>, 細見健二<sup>B</sup>, 池野正弘<sup>CD</sup>, 内田智久<sup>CD</sup>

SNPスクール2017@福島

### Outline

- Motivation

- Developed items

- Hardware

- Tapped delay line in FPGA

- Calibration

- Performance evaluation

- Summary

### Motivation

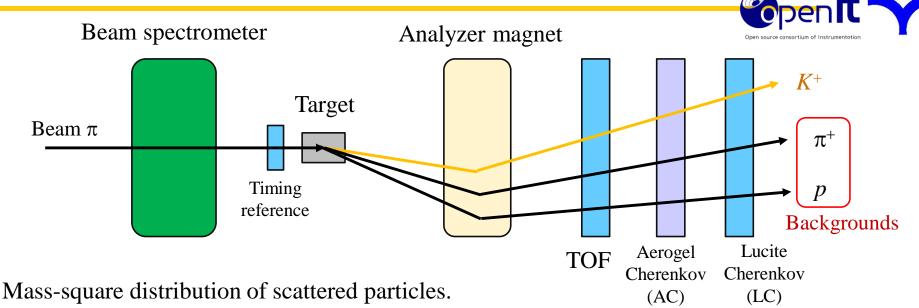

3500 Background proton Proton 3000 are rejected by 2<sup>nd</sup> level trigger 2500 2000 Counts triggered by 1<sup>st</sup> level 1500 triggered by 2<sup>nd</sup> level 1000 500 Pion Kaon 0.4 0.8 0.20.6 Mass<sup>2</sup> [GeV/c<sup>2</sup>]

- 1<sup>st</sup> level trigger : Coincidence of detector signals

- Cherenkov detectors play important role.

- **2<sup>nd</sup> level trigger** : Trigger based on time-of-flight

- High-resolution time-of-flight information is necessary.

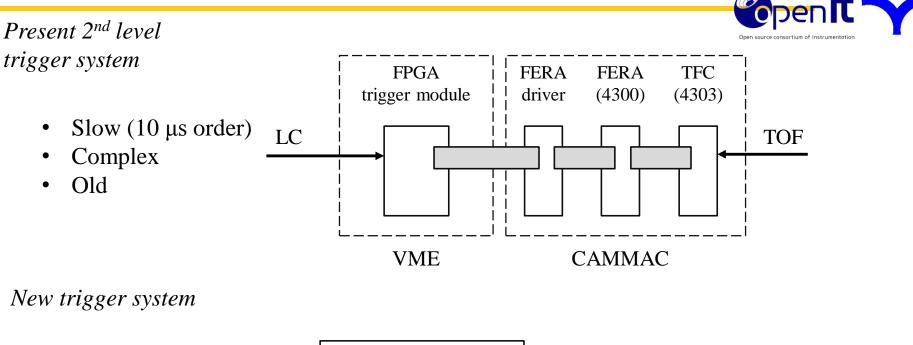

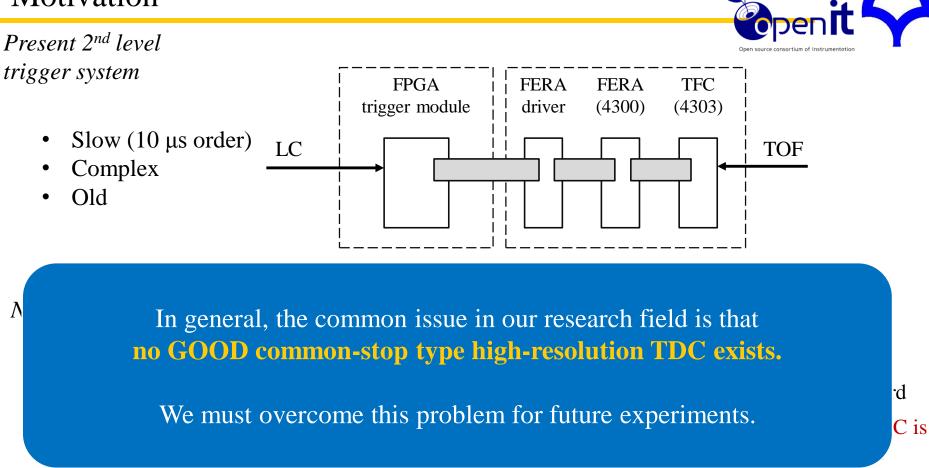

# Motivation

- Fast (100 ns order)

- Simple

FPGA based high-resolution TDC mezzanine card Development of FPGA based HR-TDC is main motivation of this project. FPGA Trigger controller module (Mother module)

Supported by Grant

新学術 (中性子星核物質) 公募研究

「J-PARC二次ビーム高強度化のための汎用トリガーモジュールの開発」

### Motivation

Trigger controller module (Mother module)

Supported by Grant 新学術 (中性子星核物質) 公募研究

「J-PARC二次ビーム高強度化のための汎用トリガーモジュールの開発」

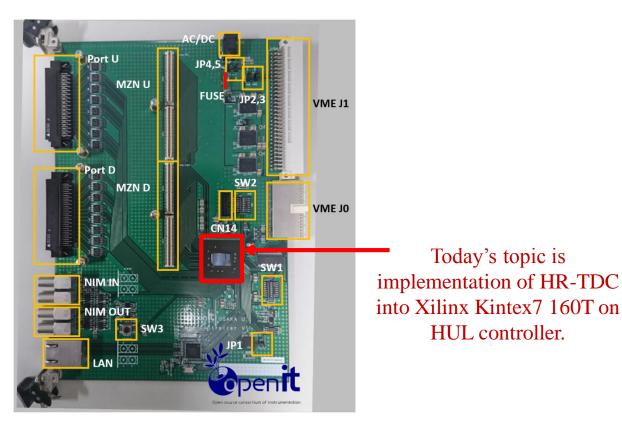

Hadron universal logic (HUL) controller module

#### HUL mezzanine cards

This project is technically supported by Open-It. http://openit.kek.jp/project/HUL/public/hul

- 64ch ECL/LVDS inputs

- Two mezzanine slots

- GbE : SiTCP (VME communication is not supported)

- Powered by J1 or AC adaptor (5V)

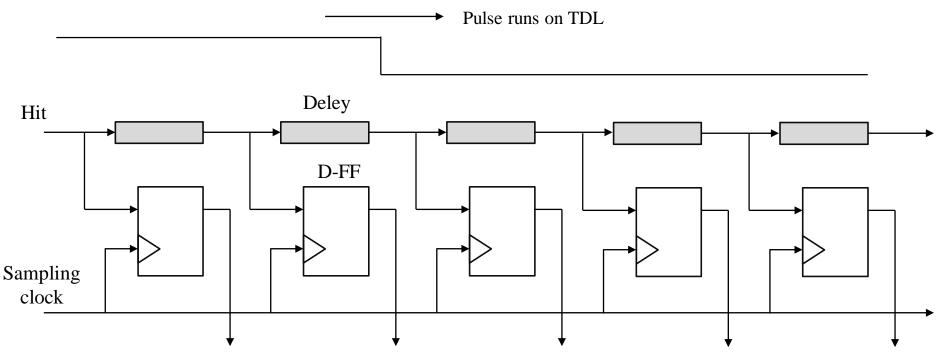

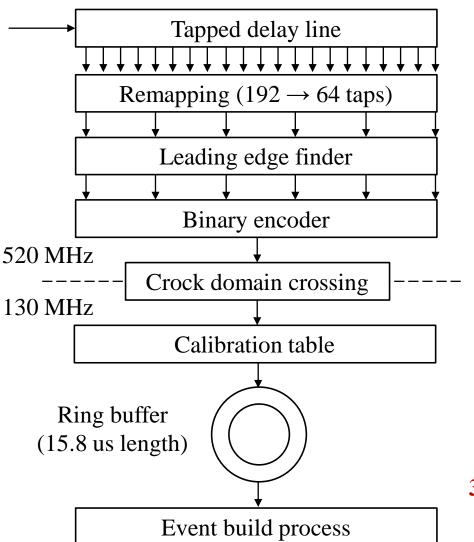

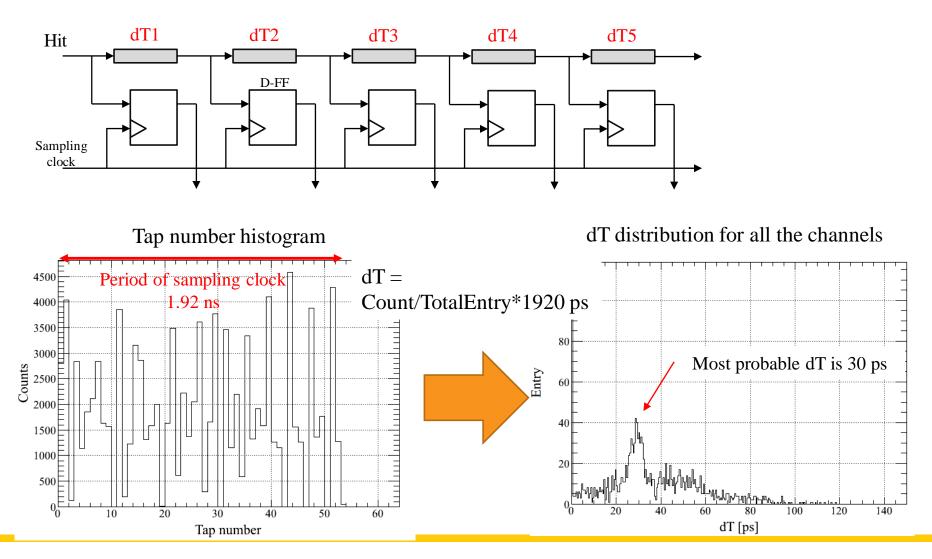

#### Tapped Delay Line (TDL)

D-Flip-Flop captures the snapshot of the pulse running on TDL.

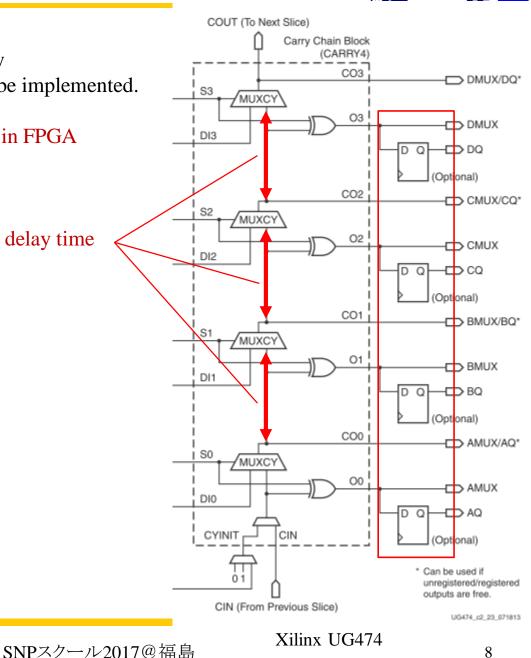

# Implementation of TDL into FPGA

FPGA : Field-Programmable Gate Array

Gate level logic coded by users can be implemented.

Implement TDL using carry line in FPGA

Carry line

- **Basic function of Adder**

- Smallest delay element with 5-30 ps delay time

- Close to FF

- Cascadable

####

#### 1111100000

0000100000

5

: Fine count + Semi coarse count (2bit) + Coarse count (11bit)

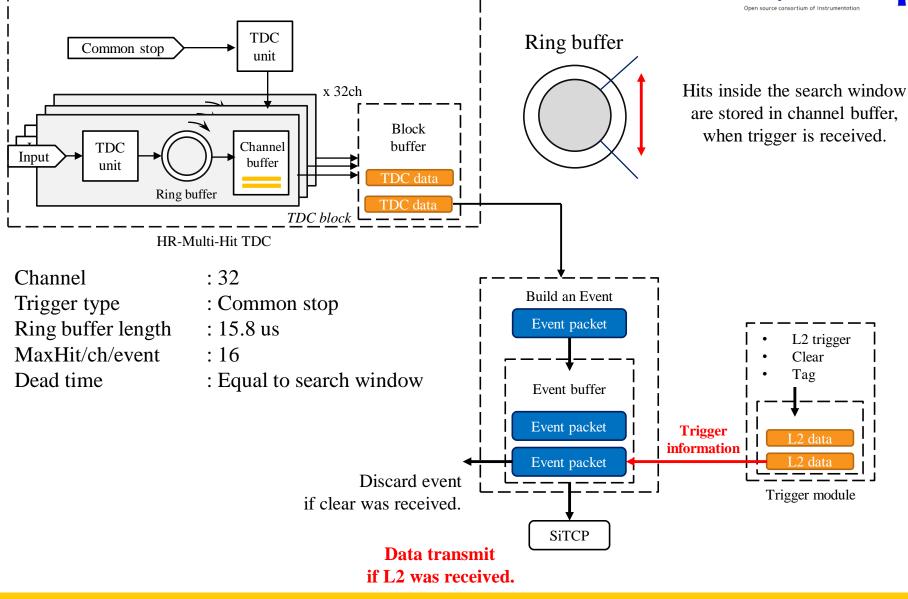

# **32ch HR-Timing unit and DAQ functions** were fully implemented into Kintex7 160T.

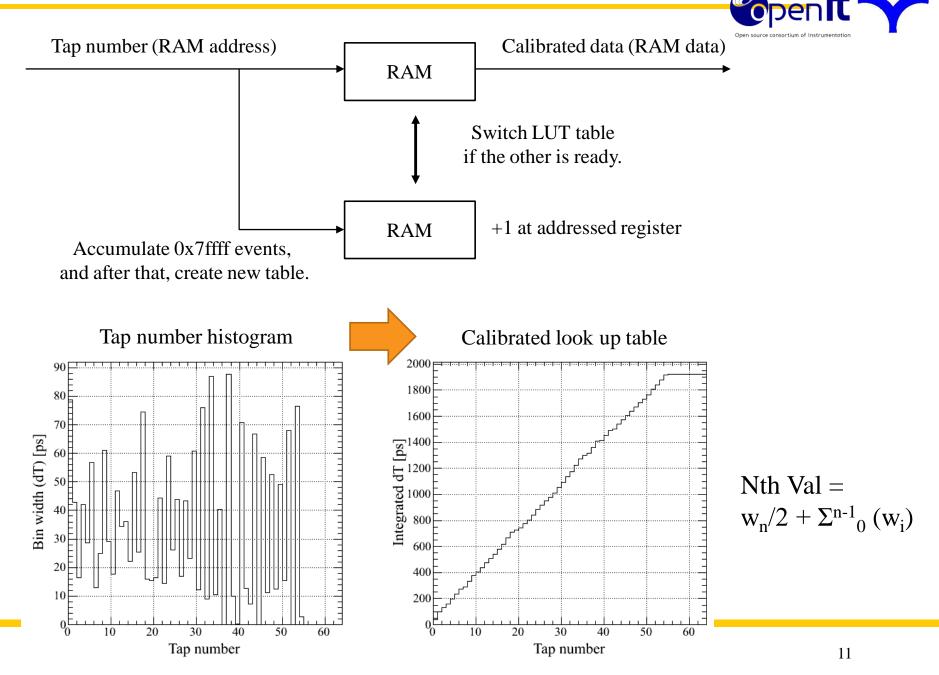

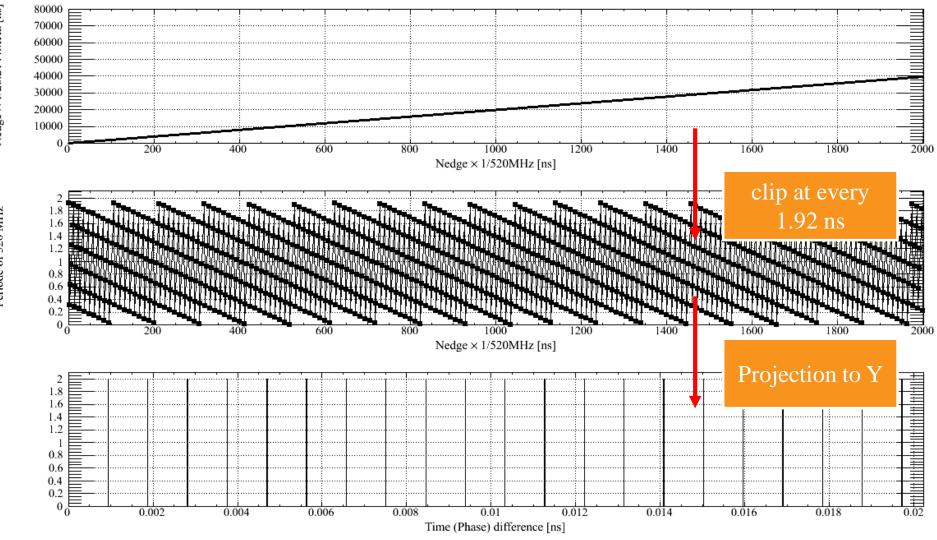

Delay time (dT) is not constant.

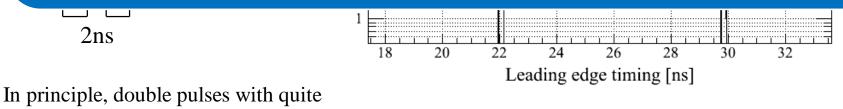

SNPスクール2017@福島

- Use detector signal.

- Corresponding to that the clock sampling of the detector signal. The detector signal must be random.

- Use clock.

- The TDC clock is 520 MHz ( $f_{sample}$ ) and calibration clock is 26.2144 ( $f_{calib}$ )

- $N^*(f_{sample}/f_{calib}) = N^*(2^{9*57*13})/(2^{20*52}) = N^*(5^{5*13})/2^{11}$

- 2048 different clock phases appear

### DAQ functions

# Performance evaluation

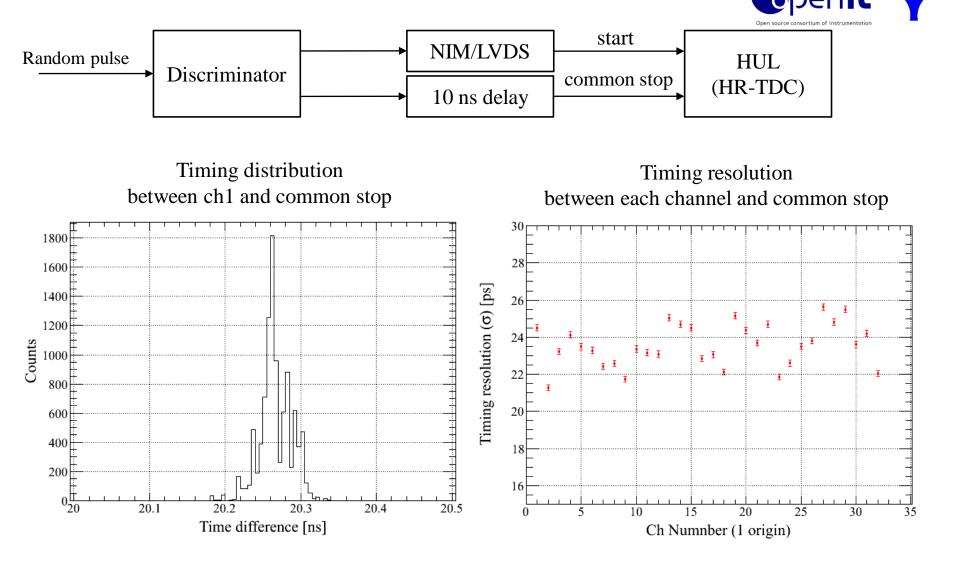

### Timing resolution

Timing resolution better than 30 ps ( $\sigma$ ) achieved for all the channel !

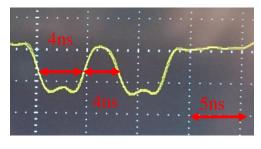

#### Input pulse

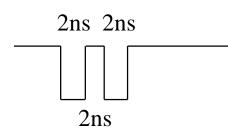

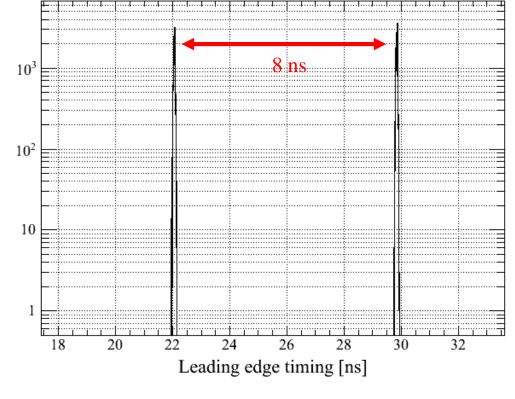

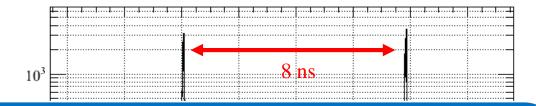

Double pulse could be measured with 100% efficiency.

In principle, double pulses with quite short interval can be measured .

#### Measured timing distribution

#### Input pulse

#### Measured timing distribution

High-resolution multi-hit TDC was successfully developed.

#### We overcame HR-TDC problem in our field !

short interval can be measured.

#### ToDo

Implement both leading and trailing edges measurement.

• At present, 8ch leading/trailing measurement was achieved.

Implement HR-TDC to FPGA on mezzanine card.

- Separate HR-TDC part from the DAQ functions.

- Customization of DAQ functions can be easy.

# Future possibility

- Synchronization with master clock

- Implement as free-run type TDC

New mezzanine card for HR-TDC (Same FPGA is mounted)

- Develop the 2<sup>nd</sup> level trigger system using FPGA based HR-TDC for the *K*<sup>+</sup> selection in J-PARC experiments.

- Furthermore, FPGA based HR-TDC solve the problem that no good HR-TDC exists in our research field.

- Tapped delay line HR-TDC, which realized by carry line, was implemented into Xilinx Kintex7 160T.

- 32ch HR-TDC unit and DAQ functions were fully implemented.

- The timing resolution better than 30 ps ( $\sigma$ ) was achieved for all the channel.

- The double-hit resolution was at least 8 ns.

- We overcame the HR-TDC problem by this development.

# Backup

SNPスクール2017@福島

# Principle of calibration using clock.

open

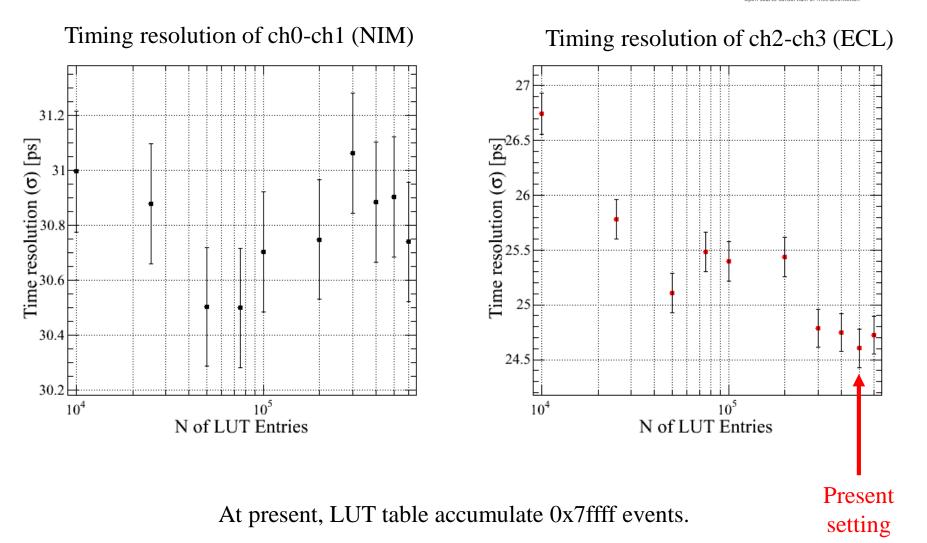

# LUT Entry dependence of timing resolution

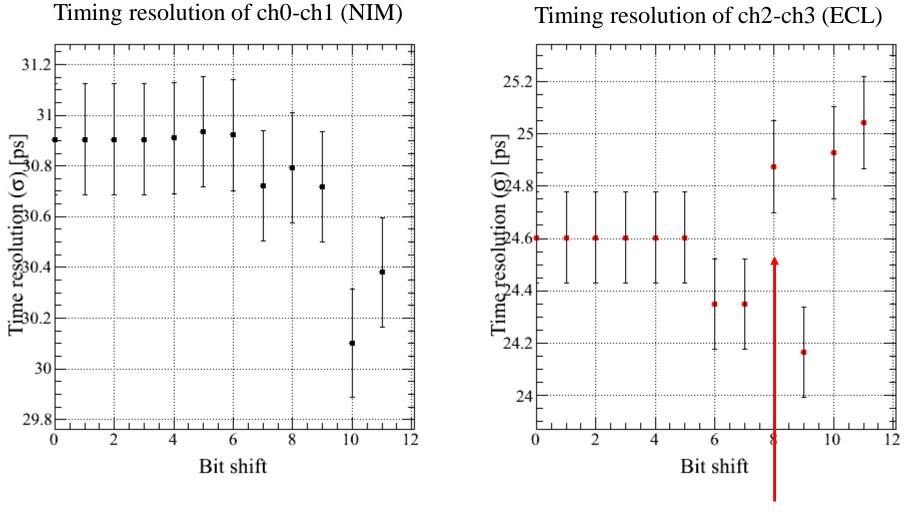

Bit length dependence of timing resolution

At present, lower 8bits are discarded.